随着人工智能技术的快速发展,神经网络模型变得越来越复杂,对计算能力的需求呈指数级增长。传统CPU架构在处理神经网络计算时效率有限,神经网络硬件加速器应运而生,成为推动AI应用落地的关键技术。本文将从架构设计和技术开发两个维度深入探讨神经网络硬件加速器。

一、神经网络硬件加速器架构设计

1. 主流架构类型

- 专用集成电路(ASIC)架构:如Google的TPU、华为的昇腾系列,专门为神经网络计算优化,具有最高的能效比

- 现场可编程门阵列(FPGA)架构:如Xilinx的Versal系列,提供灵活性,支持算法迭代更新

- 图形处理器(GPU)架构:如NVIDIA的Tensor Core GPU,兼具通用性和高性能

- 神经形态计算架构:模拟生物神经网络,具有极低功耗特性

2. 核心架构组件

- 张量处理单元(TPU):专门针对矩阵乘法和卷积运算优化

- 内存层次结构:多级缓存设计,减少数据搬运开销

- 数据流控制器:实现计算与数据搬运的并行化

- 互联架构:支持多核协同计算的高速互联网络

3. 架构优化策略

- 数据复用优化:通过数据局部性原理减少内存访问

- 计算并行化:充分利用空间和时间并行性

- 精度可配置:支持混合精度计算,平衡精度与性能

- 功耗管理:动态电压频率调节等低功耗技术

二、神经网络硬件加速器技术开发

1. 开发流程与方法论

- 需求分析阶段:明确目标工作负载和性能指标

- 架构探索阶段:通过建模和仿真确定最优架构

- RTL设计与验证:使用硬件描述语言实现设计

- 物理设计与流片:完成布局布线和芯片制造

- 系统集成与测试:软硬件协同验证和性能调优

2. 关键技术挑战

- 内存墙问题:计算单元与内存带宽不匹配

- 功耗约束:在有限功耗预算内实现高性能

- 编程模型:降低开发难度,提高易用性

- 可扩展性:支持不同规模的计算需求

3. 开发工具链

- 高级综合工具:如Xilinx Vitis HLS、Intel HLS

- 神经网络编译器:如TVM、MLIR

- 性能分析工具:提供详细的性能剖析和瓶颈分析

- 验证平台:确保功能正确性和性能达标

三、发展趋势与未来展望

神经网络硬件加速器正朝着更高效、更灵活、更智能的方向发展:

- 异构计算融合:CPU、GPU、专用加速器协同工作

- 存算一体架构:突破内存瓶颈的新型计算范式

- 可重构计算:根据工作负载动态调整硬件结构

- 算法-硬件协同设计:软硬件深度优化提升整体效率

四、开发实践建议

对于开发者而言,成功开发神经网络硬件加速器需要:

- 深入理解神经网络计算特征和数据流模式

- 掌握现代数字电路设计和验证方法

- 熟悉EDA工具链和开发流程

- 关注行业最新技术动态和标准演进

- 建立跨学科团队,融合算法、硬件、软件专业知识

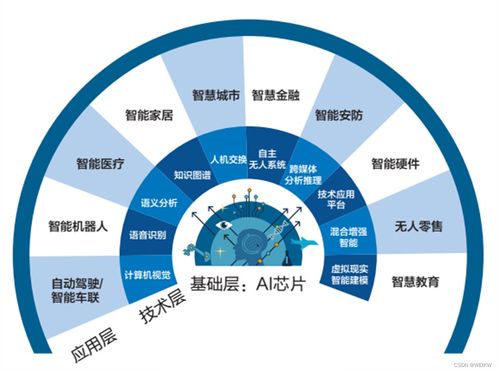

神经网络硬件加速器的架构创新和技术突破将持续推动人工智能技术的发展,为各行各业带来革命性的变革。随着技术的成熟和成本的降低,专用AI加速器将在边缘计算、自动驾驶、智能物联网等领域发挥越来越重要的作用。